科研动态

微电子所在计算光刻研究方面取得显著进展

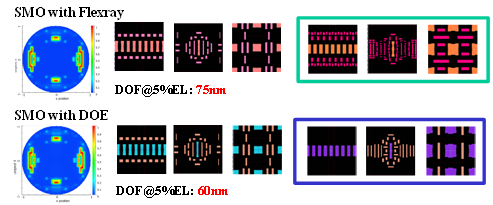

稿件来源: 发布时间:2016-03-31光源和掩模联合优化是分辨率增强技术中进一步提高光刻分辨率的关键技术。SMO根据光刻光学成像模型,采用预畸变方法调整光源形状及强度分布、修正掩模图形,调制透过掩模的电磁场分布,从而提高光刻系统的成像性能。基于该技术,课题组与美国赛普拉斯、武汉新芯合作进行“3D-NAND存储器关键层光刻条件确定”项目研发,提出了新型的光源、掩模、设计规则优化方法,进行了相应的实验研究,不仅确保了3D-NAND典型层的成功制造,而且保证了单次曝光工艺窗口达到100纳米,MEEF小于6,缺陷数量在可控范围内,曝光结果满足工业制造良率要求,解决了光刻工艺窗口过小的问题。

图1. 3D-NAND VIA1光刻关键层SMO确定最佳光刻条件

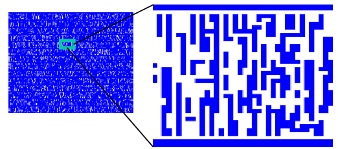

随着集成电路工业发展到20纳米节点以下,传统的设计师与制造厂之间的单线联系已不足以支撑发展,设计和工艺联合优化这一新技术理念应运而生。设计与工艺联合优化是目前光刻技术,乃至整个芯片制造技术的核心技术。标准的设计与工艺联合优化方法在我国仍是空白。目前该方面的研究和应用暂时处于不成熟的探索阶段。课题组对10纳米节点的应用开展了系统研究,提出了设计规则的转换、版图分析、模型验证、热点分类以及设计规则优化等新的方法论,通过优化设计规则生产适于14/10纳米技术节点的友好版图,以用于先进节点工艺探索与模型建立的研发。该研究进展被选为2016年中国半导体技术大会的邀请报告。

图2. 10nm节点大规模随机版图

光刻工艺稳定性控制是22纳米及以下技术节点面临的关键问题,其中焦面位置变化的高精度检测是实现工艺稳定性良好控制的重要指标。针对现有基于相移掩模的焦面位置检测方法的精度无法满足先进光刻工艺需求的问题,课题组创新性地在掩模测量标记的结构中引入透光区、阻光区、180°相移区和90°相移区四种结构(图3)。利用优化的四种结构宽度比例消除了衍射级次中的+1级和+2级,顺利解决了传统方法在超大NA光学系统中灵敏度系数低的问题,成功将焦面位置检测灵敏度提高到了![]() 。

。

相比现有方法,新型焦面位置测量标记将检测灵敏度提高了25%以上。

图3. 新型焦面位置测量标记结构示意图

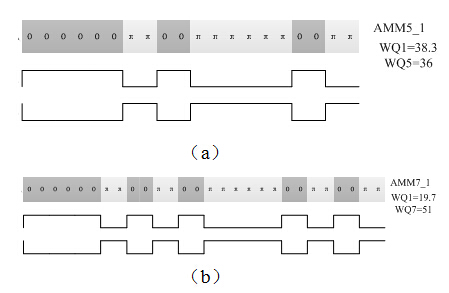

高精度光刻套刻对准决定了核心芯片的光刻质量。课题组就产业界提出的先进光刻套刻对准晶圆质量(WQ)问题进行了攻关,成功开发出面向先进光刻工艺的光刻套刻对准仿真平台,顺利解决了不同探测波长、不同薄膜图层、不同套刻结构对套刻WQ的影响。该仿真结果与193纳米光刻机实际量测结果相符,与先进计算光刻某专用商业软件仿真结果一致。课题组进一步采用简化仿真算法,提出了几种新的套刻标记(见图4),比ASML设计的AH53和AH74衍射对准标记具有更高的第一级、第五级或第七级衍射光强,即新的设计结构具有更高的套刻对准WQ,可获得更可靠的晶圆套刻质量。该成果已申请专利。

图4. 具有更高对准精度的套刻光栅单周期精细结构示意图:(a)同时兼顾一级和五级衍射光强的光栅单周期精细结构;

(b)同时兼顾一级和七级衍射光强的光栅单周期精细结构

上述研究成果得到了合作单位武汉新芯、美国赛普拉斯以及计算光刻软件商ASML和Mentor Graphics的高度认可,为产业发展做出了重要贡献。

科研工作